L'équipe de recherche de l'Institut international de quantique de Shenzhen a récemment démontré un processeur quantique à base de silicium capable d'exécuter un ensemble complet d'opérations de portes logiques universelles. Ce processeur a réalisé pour la première fois la caractérisation d'opérations logiques universelles sur une plateforme de spin de silicium, offrant une nouvelle voie pour le développement du matériel informatique quantique.

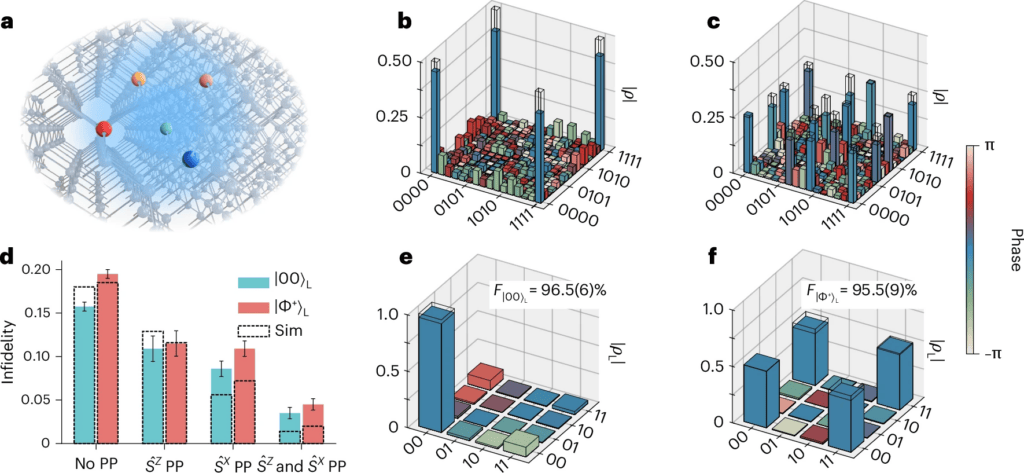

Le dispositif est basé sur cinq spins nucléaires de donneurs de phosphore, qui sont intégrés dans un réseau de silicium-28 purifié isotopiquement et structurés avec une précision atomique par une technique de lithographie à microscope à effet tunnel. Pour faire face au bruit environnemental, le système utilise un code de détection d'erreurs quantiques [[4, 2, 2]], encodant deux qubits logiques avec quatre qubits physiques. Cette architecture de processeur quantique à base de silicium attire l'attention en raison de sa compatibilité avec les procédés de fabrication standard des semi-conducteurs.

Sur le plan technique, l'équipe de recherche a caractérisé un ensemble universel de portes logiques, incluant les portes Clifford à un qubit, la porte de Hadamard simultanée et la porte CNOT à deux qubits. La porte T non-Clifford est réalisée par une méthode de mesure de porte, impliquant un spin nucléaire auxiliaire pour injecter une rotation de phase. Les données expérimentales montrent une fidélité moyenne des portes physiques supérieure à 95 %, avec un temps de cohérence logique d'environ 208 microsecondes. Le système présente un biais de bruit significatif, où les erreurs de renversement de phase dominent les erreurs de renversement de bits, ce qui pourrait réduire les exigences matérielles des architectures tolérantes aux fautes à grande échelle.

Pour évaluer l'utilité du processeur, les chercheurs ont appliqué l'algorithme du solveur variationnel quantique d'états propres pour calculer l'énergie de l'état fondamental d'une molécule d'eau (H2O). En utilisant trois techniques d'atténuation des erreurs – vérification de parité, ajustement Clifford et vérification de symétrie – l'écart moyen d'énergie par rapport à la valeur théorique était de 22,7 mHa. Ce résultat confirme la faisabilité d'exécuter des algorithmes quantiques pratiques sur des qubits logiques en silicium. Les travaux futurs se concentreront sur la réduction de la diaphonie entre les amas de donneurs et sur l'extension de l'architecture pour s'adapter à des schémas de correction d'erreurs plus complexes.